1. 概述

SDR-B1是正旗通信推出的软件无线电平台,采用Xilinx Zynq XC7Z045及ADI AD9363/AD9361。在原始的硬件设计中,SDR-B1的PS采用了33.333MHz的输入时钟频率,这也是参考设计采用的输入时钟频率。然而,近期有客户提出需要使用50MHz的输入时钟频率,本文给出修改PS输入时钟频率的方法。该方法不仅适用于正旗通信SDR-B1,也同样适用于其他采用Zynq SoC的硬件平台。由于该方法的实施过程与已有的用户指导大同小异,因此本文不再详细阐述完整过程,只给出关键步骤,其他细节可以参照《SDR-B1使用EEPROM存储MAC地址的方法》。

2. 修改Vivado工程

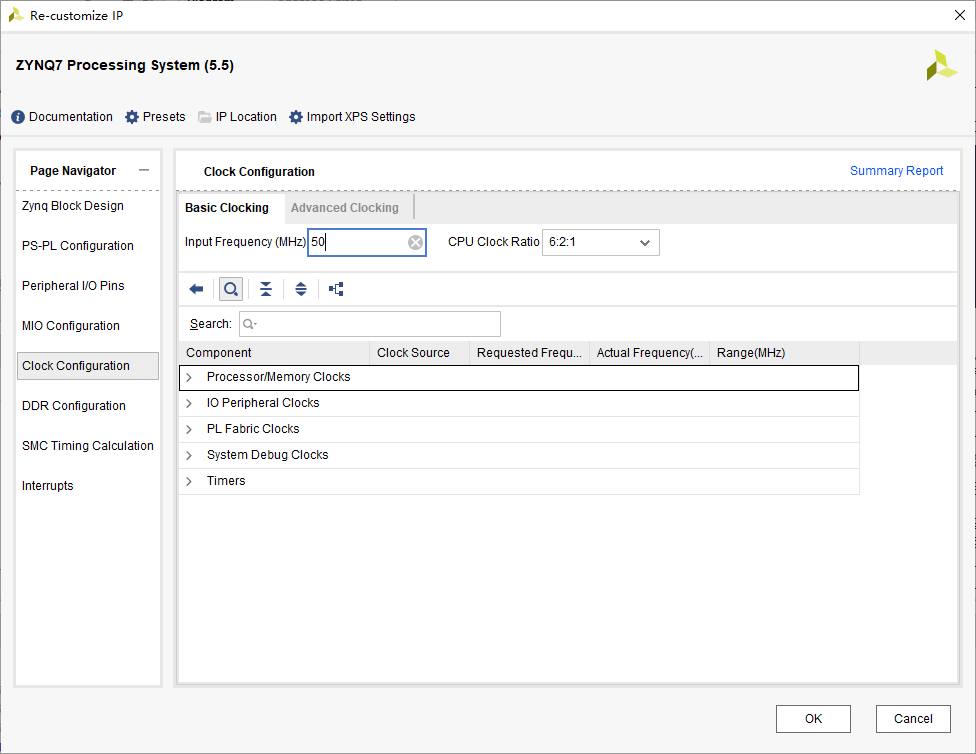

(1) 打开已有Vivado工程后,进入system.bd框图,然后双击ZYNQ将其输入时钟频率修改为50MHz,如下图

(2) 重新Generate Output Products,重新Generate Bitstream,然后将得到的system_top.bit,system_top.hdf复制到Linux准备用于Petalinux工程。

3. 修改Linux代码

(1) 修改arch/arm/boot/dts/zynq.dtsi,将ps-clk-frequency修改为50000000,然后生成补丁0002-dts-eeprom-and-50mhz-clk-by-zencheer.patch。

(2) 使用此前得到的system_top.bit,system_top.hdf创建新的Petalinux工程sdr_b1_v12_50m,将0002-dts-eeprom-and-50mhz-clk-by-zencheer.patch放置于project-spec/meta-user/recipes-kernel/linux/linux-xlnx/目录下。

(3) 在project-spec/meta-user/recipes-kernel/linux/下创建linux-xlnx_%.bbappend,将其内容改为

SRC_URI_append += "file://0002-dts-eeprom-and-50mhz-clk-by-zencheer.patch"

FILESEXTRAPATHS_prepend := "${THISDIR}/${PN}:"这样在内核编译的过程中就可以打上这个补丁。

(4) 使用petalinux-build命令编译、打包,得到BOOT.bin及image.ub,将这两个文件复制到TF卡中,板卡可正常运行。

4. 注意事项

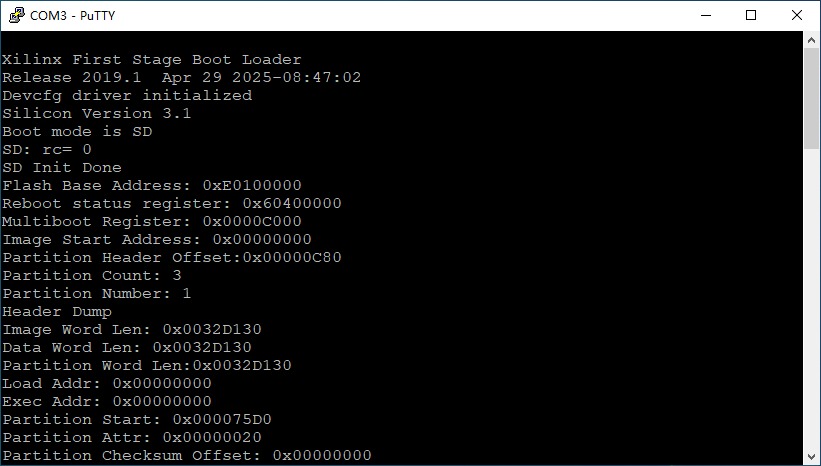

请注意,在u-boot源码中也存在zynq.dtsi文件,实际测试修改u-boot下的zynq.dtsi并不生效。这一点可在开启FSBL Debug功能后体现出来,现象为FSBL串口输出正常,而进入u-boot后,串口输出为乱码。

附:Petalinux下开启FSBL Debug的方法

修改project-spec/meta-plnx-generated/recipes-bsp/fsbl/fsbl_%.bbappend,增加以下内容

XSCTH_BUILD_DEBUG = "1"然后使用以下命令重新编译FSBL

petalinux-build -c fsbl -x distclean

petalinux-build -c fsbl再次打包得到BOOT.bin及image.ub,复制到TF卡中,启动板卡后即可输出FSBL的Debug信息,如下图