1. 概述

我司产品中通常会有大量的射频电路存在,因此射频电路设计是我司产品设计的重点。按功能划分,射频电路可以分为:ADC/DAC、本振、混频器、增益模块、射频功率放大器、低噪声放大器、滤波器、射频开关等。

2. 射频电源电路

小信号射频电路推荐采用LDO供电,如ADC/DAC、本振、混频器及低噪声放大器,或者是专用宽带收发无线芯片,如AD9361。

大信号电路推荐采用DCDC供电,如增益模块,射频功率放大器。

在Layout方面,DCDC要远离射频电路,尤其是ADC/DAC、本振、混频器、低噪声放大器等小信号电路,如果条件允许,最好为DCDC设计屏蔽罩或者屏蔽腔体。LDO可以靠近相应的芯片进行摆放。

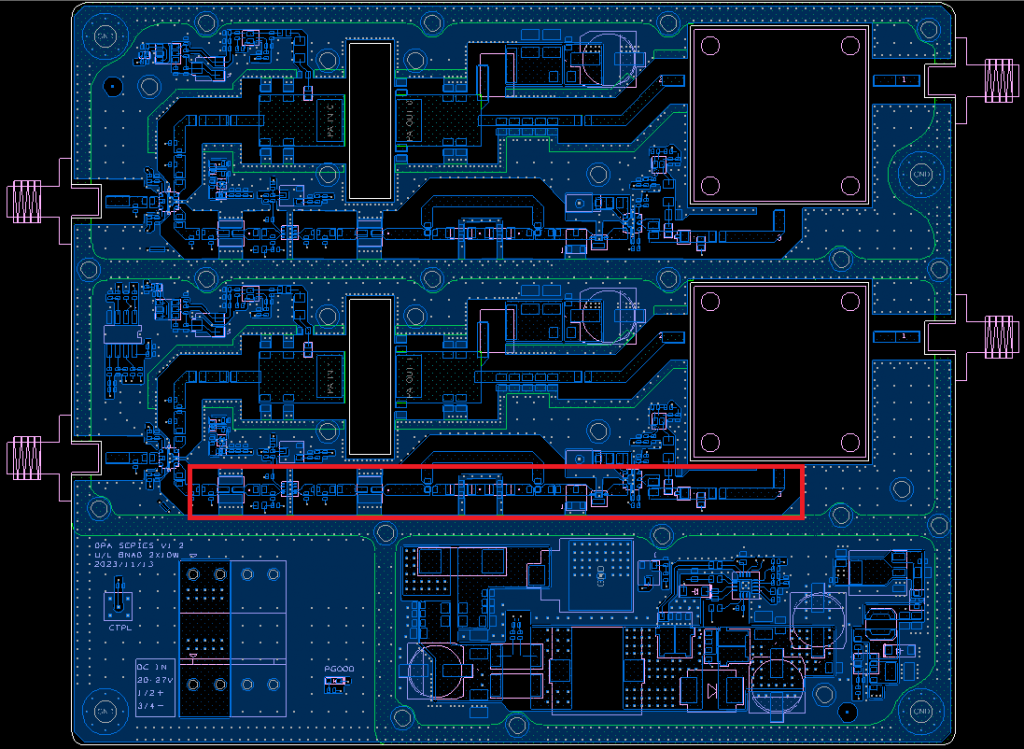

我司的一款射频功放DPA-10,在早期版本中,LNA靠近DCDC Boost摆放,实测中发现在不盖盖子的情况,有一路接收机收到严重干扰,如下图。

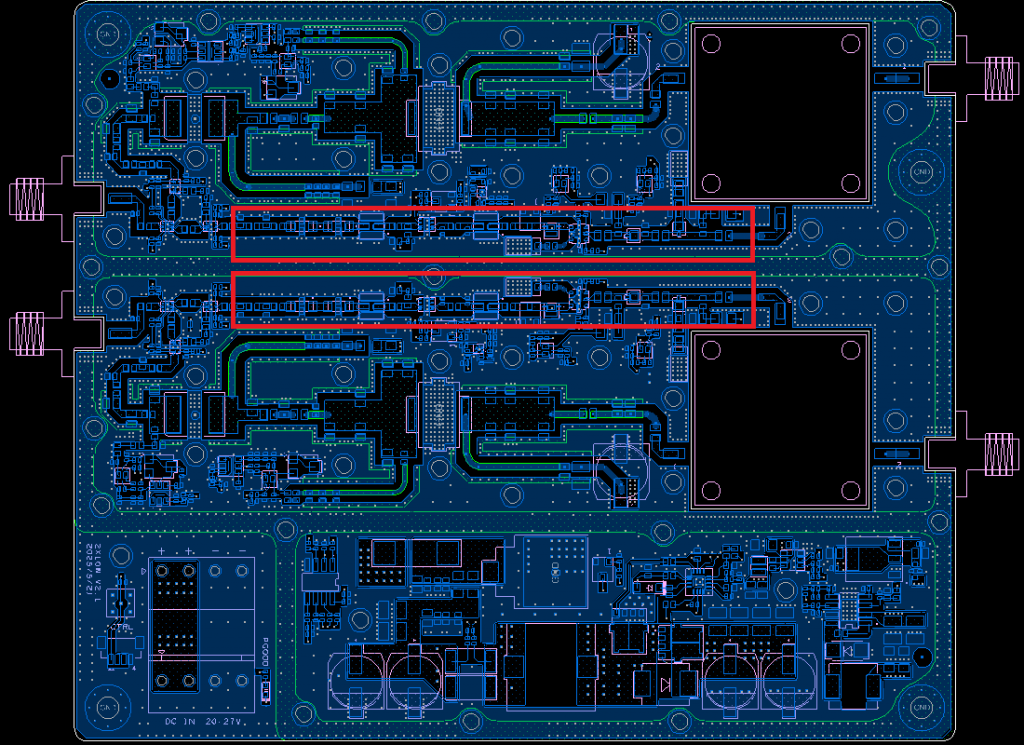

在DPA-HG-10的设计中,则在DPA-10的基础上做了较大修改,将DPA-10中出现问题的LNA远离DCDC Boost,问题得到解决。

下图是改进后的设计。

3. 射频电路Layout一般规则

- 射频走线必须有完整的、连续的参考面。

- 射频走线必须做50ohm阻抗控制,尤其是大功率射频信号。

- 射频电路走线应该尽量短。

- 去耦电容应尽量靠近相应的引脚。

- 射频走线不要出现尖角,尽量用弧线进行转弯,或者采用切角的方式进行转弯,切角的设计需要使用ADS进行仿真。

- 射频走线尽量不要使用过孔。

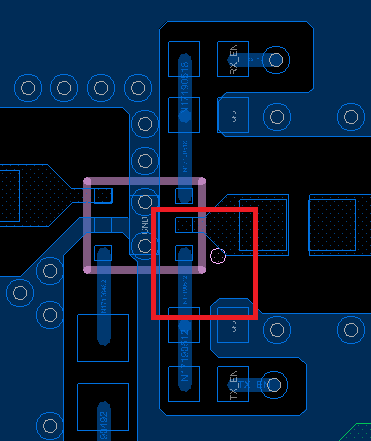

- 射频走线最好被GND铜皮包围,与铜皮做2W线距控制,并在铜皮上打上足够多的过孔。靠近芯片引脚的位置,必然无法按2W控制,此时可按照渐变的方式进行设计,如下图。

- 混频器、射频放大器,需要尽量增大输入与输出的距离,避免震荡。

4. LDMOS栅极驱动电路

LDMOS的输出特性与LDMOS栅极驱动电路密切相关。在我司早期的产品中,使用模拟开关驱动LDMOS栅极,有如下特征:

- 出现低频段杂散,谱线的位置随机,但可以观察到一定的分布特性。

- 开关频率越高,谱线越密;开关频率越低,谱线越稀疏。

- 更改开关占空比,谱线分布无明显变化。

- 栅极电压越高,谱线幅度越高。

- 将LDMOS关断电压设置为略低于LDMOS打开的临界点,谱线幅度大大降低。

客户反馈产品有很大的输出杂散后,我司使用NMOS+PMOS作为LDMOS栅极驱动电路,则不存在以上问题,LDMOS输出正常。下图是我司使用的标准LDMOS栅极驱动电路。

5. 射频连接器

避免MMCX与IPX co-layout。

产品工作频率在1.5GHz以下时,可以使用直插式射频连接器;高于1.5GHz的例如2.4GHz尤其是5.8GHz的情况,必须使用贴片式连接器,至少中心角是贴片的形式。

6. 温补晶振

经过长期检验,KDS的TCXO质量很好,如DSB321SDN系列。

7. GPS外接天线

必须为GPS外接天线做限流设计。